WSP(웨이퍼스택패키지)

|

칩간 연결 중간층 최소화 … 관통전극 구현

레이저로 구멍 뚫어 칩간 선 없애

전체두께는 줄고 동작속도 30% 향상

대용량 고성능 첨단칩으로 '일석삼조'

최근 삼성전자가 세계 최초로 관통전극형(Through Silicon Via) 칩 접속 방식인 WSP(Wafer-Level Processed Stack Package) 기술을 적용한 4단 적층 D램 칩과 모듈 개발에 성공해 이 기술에 관심이 고조되고 있습니다.

WSP는 반도체의 후공정 중 하나인 패키징(반도체에 옷 입히기)에 일대 혁신을 가져온 기술입니다.

과거 다중칩패키지(MCP) 등의 공정에서 금선(Gold Wire)으로 칩 사이를 연결하던 것을 대신하는 방법으로, 세계 최초로 여러 겹의 웨이퍼를 레이저로 구멍을 뚫고, 그 구멍을 전자전도도가 높은 구리로 메워 위아래 칩이 전기적으로 연결되도록 하는 것입니다.

전세계 반도체 기업들은 더 좁은 공간에 더 큰 용량과 다양한 기능을 가진 칩을 넣기 위해 치열한 경쟁을 펼치고 있습니다. 이런 이유로 칩간 연결을 하는 중간층조차 줄이기 위한 노력의 일환으로 WSP 기술을 개발한 것입니다.

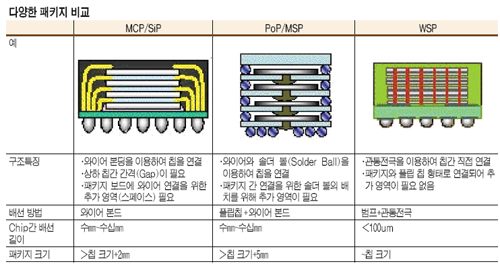

이 WSP는 웨이퍼를 수직으로 관통하는 홀(Hole)을 통해 `칩간 직접 접속`을 하는 방식입니다. 기존 MCP 기술은 칩 상하간에 수십 마이크론의 간격이 필요하고, 패키지 보드에 와이어 연결을 위한 추가적인 공간이 필요했었습니다.

삼성이 개발한 이번 WSP 기술의 핵심인 관통전극 구현을 위해 일반적인 드라이 에칭(Dry Etching) 대신 삼성 독자기술인 레이저 드릴링(Laser Drilling) 방식을 채택, 포토ㆍ에칭 등 `패터닝' 공정을 생략함으로써 제조원가 크게 절감할 수 있었습니다.

이 기술을 적용할 경우 칩간 공간이 불필요해 전체 두께를 MCP 제품 대비 30% 줄이고, 실장면적도 15% 가량 축소할 수 있게 됐습니다. 또한칩 연결을 위한 배선에 고밀도 쇼트와이어(Short Wire)를 적용해, 전자가 이동하는 거리를 줄임으로써 동작속도도 30% 이상 빨라졌습니다.

패키지를 줄이면서 대용량 고성능의 최첨단 복합칩 솔루션을 가지게 됐으니 `일석삼조'라고할 수 있지요.

삼성전자는 지난해 4월에 이 기술을 적용해 50마이크론 두께의 2Gb 낸드 플래시 8개를 적층해, 전체 두께가 560마이크론에 불과한 두께가 가능했습니다. 그리고 이번에는 D램에도 이 기술을 적용해 512Mb DDR2 D램을 4개 적층한 2Gb 대용량 D램 적층 단일칩과, 이 칩을 앞뒷면으로 8개씩 총 16개를 붙인 4GB 모듈을 개발했지요.

이번에 개발된 D램의 경우 낸드보다 회로가 복잡하게 형성돼 있어 웨이퍼를 얇게 할 경우 웨이퍼 휨 현상(Warpage)이 더욱 잘 발생하는데 삼성전자는 작년 11월에 개발 성공한 16단 MCP 패키지에 적용된 웨이퍼 박막화 기술을 활용해 D램 WSP를 구현했지요.

시스템에 적용되는 반도체의 고성능화를 위해서는 단품 칩 개발도 중요하나, 수십 나노 수준까지 축소된 칩 가공 기술을 뒷받침 할 수 있는 패키지 기술의 개발 역시 수반되어야 한답니다.

지금까지는 패키지 기술이 칩 제조 기술만큼 빠른 속도로 진화하지 못하였기 때문에, 나노급까지 진화된 칩 제조 기술과 마이크로미터급의 패키지 기술간의 격차가 발생해 왔습니다.

이와 관련해 삼성전자가 주도하고 있는 차세대 패키지인 기술인 WSP는 칩 제조 기술과 패키지 기술간의 미세화 격차를 줄일 수 있도록 해 업계에서 많은 주목을 받고 있습니다.

전세계 반도체 업체들은 3차원 트랜지스터를 활용해 고용량ㆍ나노 칩 및 솔루션 개발에 나서고 있습니다. 최근에는 일본 엘피다가 WSP를 적용하지 않고 기존 MCP 기술을 이용해 20층 MCP를 개발해 기술 경쟁에 나서고 있기도 합니다.

WSP가 `더 작게 더 얇게' 칩의 패키지를 만드려는 반도체 업계의 표준으로 자리잡을지 반도체 업계의 관심이 모아지고 있습니다.

레이저로 구멍 뚫어 칩간 선 없애

전체두께는 줄고 동작속도 30% 향상

대용량 고성능 첨단칩으로 '일석삼조'

최근 삼성전자가 세계 최초로 관통전극형(Through Silicon Via) 칩 접속 방식인 WSP(Wafer-Level Processed Stack Package) 기술을 적용한 4단 적층 D램 칩과 모듈 개발에 성공해 이 기술에 관심이 고조되고 있습니다.

WSP는 반도체의 후공정 중 하나인 패키징(반도체에 옷 입히기)에 일대 혁신을 가져온 기술입니다.

과거 다중칩패키지(MCP) 등의 공정에서 금선(Gold Wire)으로 칩 사이를 연결하던 것을 대신하는 방법으로, 세계 최초로 여러 겹의 웨이퍼를 레이저로 구멍을 뚫고, 그 구멍을 전자전도도가 높은 구리로 메워 위아래 칩이 전기적으로 연결되도록 하는 것입니다.

전세계 반도체 기업들은 더 좁은 공간에 더 큰 용량과 다양한 기능을 가진 칩을 넣기 위해 치열한 경쟁을 펼치고 있습니다. 이런 이유로 칩간 연결을 하는 중간층조차 줄이기 위한 노력의 일환으로 WSP 기술을 개발한 것입니다.

이 WSP는 웨이퍼를 수직으로 관통하는 홀(Hole)을 통해 `칩간 직접 접속`을 하는 방식입니다. 기존 MCP 기술은 칩 상하간에 수십 마이크론의 간격이 필요하고, 패키지 보드에 와이어 연결을 위한 추가적인 공간이 필요했었습니다.

삼성이 개발한 이번 WSP 기술의 핵심인 관통전극 구현을 위해 일반적인 드라이 에칭(Dry Etching) 대신 삼성 독자기술인 레이저 드릴링(Laser Drilling) 방식을 채택, 포토ㆍ에칭 등 `패터닝' 공정을 생략함으로써 제조원가 크게 절감할 수 있었습니다.

이 기술을 적용할 경우 칩간 공간이 불필요해 전체 두께를 MCP 제품 대비 30% 줄이고, 실장면적도 15% 가량 축소할 수 있게 됐습니다. 또한칩 연결을 위한 배선에 고밀도 쇼트와이어(Short Wire)를 적용해, 전자가 이동하는 거리를 줄임으로써 동작속도도 30% 이상 빨라졌습니다.

패키지를 줄이면서 대용량 고성능의 최첨단 복합칩 솔루션을 가지게 됐으니 `일석삼조'라고할 수 있지요.

삼성전자는 지난해 4월에 이 기술을 적용해 50마이크론 두께의 2Gb 낸드 플래시 8개를 적층해, 전체 두께가 560마이크론에 불과한 두께가 가능했습니다. 그리고 이번에는 D램에도 이 기술을 적용해 512Mb DDR2 D램을 4개 적층한 2Gb 대용량 D램 적층 단일칩과, 이 칩을 앞뒷면으로 8개씩 총 16개를 붙인 4GB 모듈을 개발했지요.

이번에 개발된 D램의 경우 낸드보다 회로가 복잡하게 형성돼 있어 웨이퍼를 얇게 할 경우 웨이퍼 휨 현상(Warpage)이 더욱 잘 발생하는데 삼성전자는 작년 11월에 개발 성공한 16단 MCP 패키지에 적용된 웨이퍼 박막화 기술을 활용해 D램 WSP를 구현했지요.

시스템에 적용되는 반도체의 고성능화를 위해서는 단품 칩 개발도 중요하나, 수십 나노 수준까지 축소된 칩 가공 기술을 뒷받침 할 수 있는 패키지 기술의 개발 역시 수반되어야 한답니다.

지금까지는 패키지 기술이 칩 제조 기술만큼 빠른 속도로 진화하지 못하였기 때문에, 나노급까지 진화된 칩 제조 기술과 마이크로미터급의 패키지 기술간의 격차가 발생해 왔습니다.

이와 관련해 삼성전자가 주도하고 있는 차세대 패키지인 기술인 WSP는 칩 제조 기술과 패키지 기술간의 미세화 격차를 줄일 수 있도록 해 업계에서 많은 주목을 받고 있습니다.

전세계 반도체 업체들은 3차원 트랜지스터를 활용해 고용량ㆍ나노 칩 및 솔루션 개발에 나서고 있습니다. 최근에는 일본 엘피다가 WSP를 적용하지 않고 기존 MCP 기술을 이용해 20층 MCP를 개발해 기술 경쟁에 나서고 있기도 합니다.

WSP가 `더 작게 더 얇게' 칩의 패키지를 만드려는 반도체 업계의 표준으로 자리잡을지 반도체 업계의 관심이 모아지고 있습니다.

삼성전자, 신개념 반도체패키지 기술 개발

연합뉴스 입력 2006.04.13 11:21'반도체산업동향' 카테고리의 다른 글

| 인쇄회로기판(PCB) 업계는 위기, FoWLP 기술이 확산되면... (0) | 2016.11.11 |

|---|---|

| 레이저 마킹기의 기술 발전 동향 (0) | 2016.08.10 |

| D램 DDR3에서 DDR4로 본격 전환...국내 반도체 및 후방 업체들, 시장 선점 속도 낸다 (0) | 2014.10.24 |

| 반도체 실리콘 관통전극 TSV (Through Silicon Via) 기술 (0) | 2014.04.14 |

| 삼성전자, NFC 액세서리 `삼성 텍타일` 출시 (0) | 2013.03.04 |